Xilinx FPGA용 그마나 저렴한 jtag인데 64$

[링크 : https://digilent.com/shop/jtag-hs2-programming-cable/]

정품은 270$

[링크 : https://www.xilinx.com/products/boards-and-kits/hw-usb-ii-g.html]

아무튼 jtag-hs2를 연결해서 리눅스에서 보면 그냥 시리얼 포트다 (연결되었다 끊어지지만)

| $ lsusb -t -v |__ Port 2: Dev 3, If 0, Class=Vendor Specific Class, Driver=ftdi_sio, 480M ID 0403:6014 Future Technology Devices International, Ltd FT232H Single HS USB-UART/FIFO IC $ sudo dmesg [ 924.904844] usb 1-2: new high-speed USB device number 14 using xhci_hcd [ 925.059009] usb 1-2: New USB device found, idVendor=0403, idProduct=6014, bcdDevice= 9.00 [ 925.059027] usb 1-2: New USB device strings: Mfr=1, Product=2, SerialNumber=3 [ 925.059034] usb 1-2: Product: Digilent USB Device [ 925.059040] usb 1-2: Manufacturer: Digilent [ 925.059045] usb 1-2: SerialNumber: 0000000000 [ 925.066084] ftdi_sio 1-2:1.0: FTDI USB Serial Device converter detected [ 925.066178] usb 1-2: Detected FT232H [ 925.067712] usb 1-2: FTDI USB Serial Device converter now attached to ttyUSB0 [ 925.104014] ftdi_sio ttyUSB0: FTDI USB Serial Device converter now disconnected from ttyUSB0 [ 925.104066] ftdi_sio 1-2:1.0: device disconnected |

[링크 : https://www.ftdichip.com/old2020/Products/ICs/FT232H.htm]

FT232H 만은 싼데.. EVK 나 이런건 가격이 도대체 몇배가 뛰는거냐.. (억울하면 직접 만들어야?)

| 1: ₩5,301.6 25: ₩4,802.4 100: ₩4,667.5 250: ₩4,478.7 |

[링크 : https://www.mouser.kr/c/?marcom=123533426]

'embeded > FPGA - XILINX' 카테고리의 다른 글

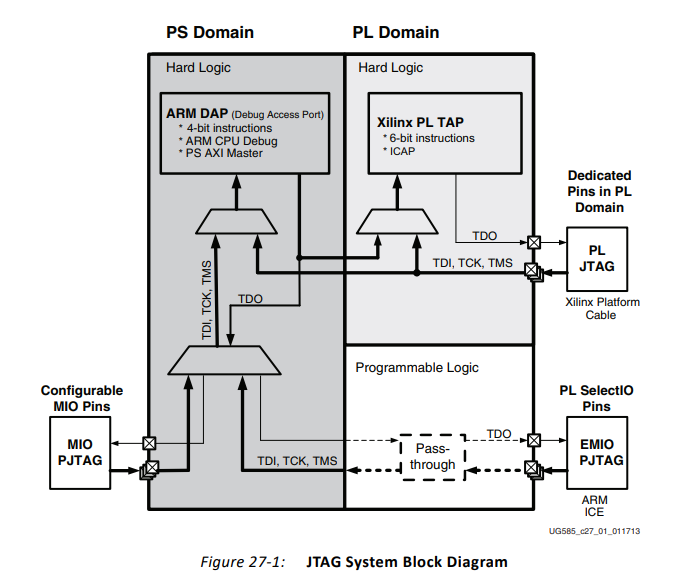

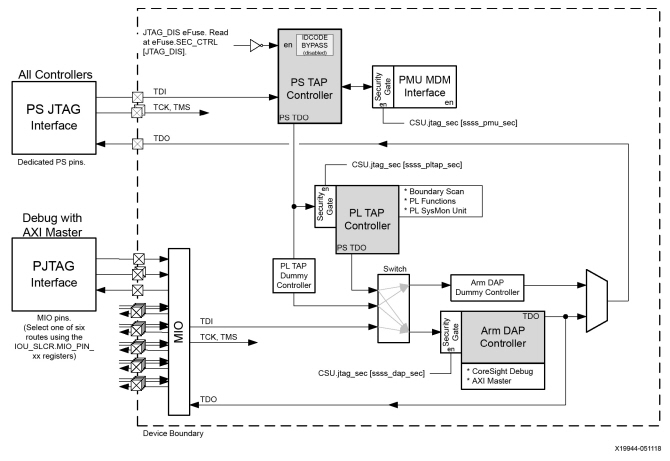

| xilinx zynq jtag (2) | 2023.07.21 |

|---|---|

| zynq 7000 fsbl (0) | 2023.07.12 |

| zynq fsbl (0) | 2023.07.07 |

| zynq w/o ps (0) | 2023.06.30 |

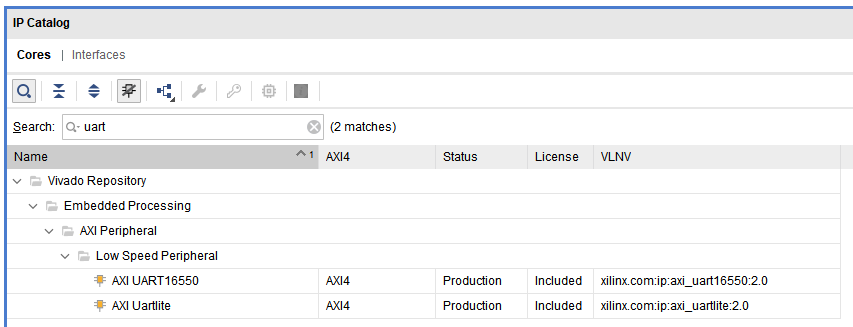

| xilinx uartlite on zynq (0) | 2023.05.16 |